基于FPGA的精密时间同步方案

1. 用途

需要通过网络实现时钟精确同步的场合,如:

基站等移动通信系统

视音频传输和处理

车联网,自动驾驶

工业控制

2. 支持标准

IEEE 1588v1

IEEE 1588v2

IEEE 802.1AS

PTP over Ethernet/UDP IPv4/IPv6

主从模式

3. 实现方案

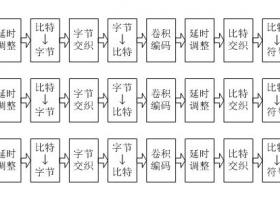

系统框图如下,实现方式根据性能和成本可以灵活决定

纯硬件(全FPGA)

软硬结合(FPGA + CPU)

纯软件(全CPU)

4. 性能数据

实现方法 同步精度

纯硬件(全FPGA) 10 纳秒

软硬结合(FPGA+ CPU) 200 纳秒

纯软件(全CPU) 10 微秒

评论

TA的案例

有10个案例

最近访客